康比電子該應(yīng)用筆記討論了如何降低振蕩器功耗,同時(shí)實(shí)現(xiàn)最佳振蕩裕度——使用石英晶體設(shè)計(jì)與節(jié)能低功耗SoC相匹配.已發(fā)表的測(cè)量結(jié)果證明了設(shè)計(jì)可靠,低功耗振蕩器的關(guān)鍵原則.隨著計(jì)算機(jī)技術(shù)和微電子技術(shù)的迅速發(fā)展,嵌入式系統(tǒng)應(yīng)用領(lǐng)域越來(lái)越廣泛.節(jié)能是全球化的熱潮,如計(jì)算機(jī)里的許多芯片過(guò)去用5V供電,現(xiàn)在用3.3V,1.8V,并提出了綠色系統(tǒng)的概念.很多廠商很注重微控制器的低功耗問(wèn)題.電路與系統(tǒng)的低功耗設(shè)計(jì)一直都是電子工程技術(shù)人員設(shè)計(jì)時(shí)需要考慮的重要因素.

振蕩器基礎(chǔ)

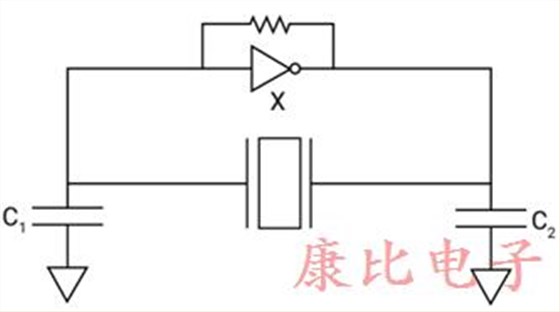

圖1-皮爾斯振蕩器框圖

對(duì)低電流,可靠晶體振蕩器的需求

對(duì)電池供電/長(zhǎng)壽命無(wú)線設(shè)備的需求正在增加.需求由越來(lái)越實(shí)惠,高能效的處理器和無(wú)線電驅(qū)動(dòng).開(kāi)發(fā)人員通常應(yīng)用超低功耗片上系統(tǒng)(SoC)無(wú)線電/處理器來(lái)支持具有多年電池壽命的小型設(shè)備.通常,這種產(chǎn)品成本和尺寸的主導(dǎo)因素是電池,電池尺寸由待機(jī)電流主導(dǎo),待機(jī)電流由低頻時(shí)鐘振蕩器主導(dǎo).

圖1顯示了大多數(shù)SoC中使用的皮爾斯振蕩器配置.振蕩器環(huán)路由反相放大器和反饋電阻(芯片內(nèi)部)以及精密相移電路組成,精密相移電路由晶體(X)和負(fù)載電容C1和C2組成.當(dāng)放大器的輸出反饋到輸入端時(shí),它會(huì)產(chǎn)生負(fù)電阻,并在正確的條件下振蕩.

眾所周知,極低功率石英晶體振蕩器會(huì)出現(xiàn)與增益不足和高晶體負(fù)載相關(guān)的啟動(dòng)問(wèn)題.為了在省電的同時(shí)避免啟動(dòng)問(wèn)題,開(kāi)發(fā)人員需要對(duì)決定待機(jī)電流和振蕩器可靠性的因素做出明智的設(shè)計(jì)決策.換句話說(shuō),振蕩器既需要汲取低電流,又必須在生產(chǎn)變化和溫度范圍內(nèi)可靠啟動(dòng).

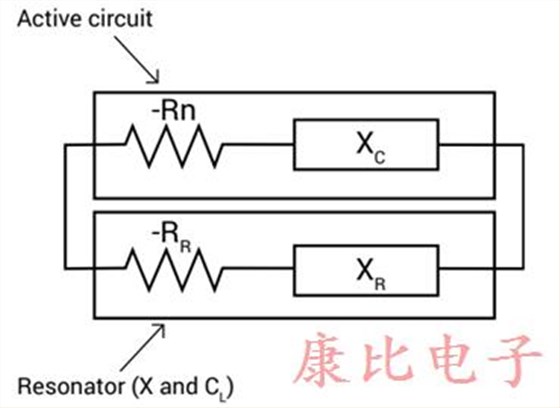

圖2-負(fù)阻振蕩器模型

由于時(shí)鐘電源效率的重要性,SoC采用了多種時(shí)鐘管理方法.本應(yīng)用筆記研究?jī)煞N最常見(jiàn)的時(shí)鐘管理方法:自動(dòng)增益控制和可選增益.了解這兩種方法如何與石英晶振特性相互作用,將支持明智的晶體選擇和相關(guān)的處理器/微控制器設(shè)置.

為了進(jìn)一步了解,圖2將振蕩器描述為負(fù)電阻(Rn),電路電抗(Xc),諧振器電抗(XR)和諧振器電阻(RR)的組合.如果Rn>RR,電路將以Xc=-XR的頻率振蕩.

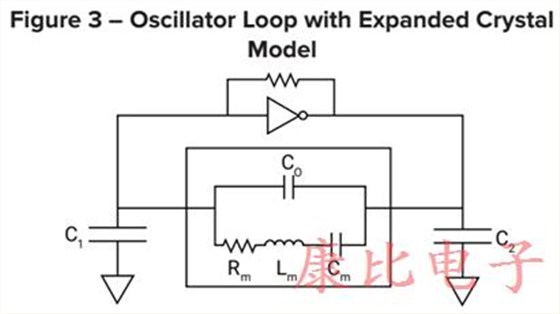

圖3顯示了一個(gè)振蕩器,重點(diǎn)是晶體等效電路.

圖4說(shuō)明了辦公自動(dòng)化的實(shí)際測(cè)量,并提供了對(duì)術(shù)語(yǔ)“辦公自動(dòng)化”有用性的洞察.這里,振蕩回路包括一個(gè)附加電阻Ra.通過(guò)增加Ra直到有源晶振振蕩器不再啟動(dòng)來(lái)測(cè)量OA,然后OA計(jì)算如下:

振蕩容限=OA=Rn/Re

Rn是負(fù)電阻Rn=Re+Ra

Re是等效串聯(lián)電阻(通常稱(chēng)為等效串聯(lián)電阻)

等效串聯(lián)電阻=Rmx(1+鈷/氯)

Rm是晶體運(yùn)動(dòng)電阻,Co是晶體封裝寄生電容,C1和C2是晶體負(fù)載/電鍍電容

(共同表示CL)Lm是晶體運(yùn)動(dòng)電感Cm是晶體運(yùn)動(dòng)電容

OA對(duì)石英晶體諧振器參數(shù)有顯著的依賴(lài)性,并且隨著Rm和CL的增加而降低.對(duì)于振蕩幅度相對(duì)較小的極低功率振蕩器,這種依賴(lài)性顯著增加.在開(kāi)發(fā)過(guò)程中,測(cè)量辦公自動(dòng)化經(jīng)常被忽略,這可能導(dǎo)致以后產(chǎn)生問(wèn)題.

振蕩裕量-預(yù)測(cè)可靠啟動(dòng)

振蕩裕量,也稱(chēng)為閉環(huán)增益裕量,是一個(gè)用來(lái)描述振蕩器可靠性的術(shù)語(yǔ),其品質(zhì)因數(shù)描述振蕩器對(duì)附加損耗的容忍度.眾所周知,小于5的OA是不可接受的,低OA會(huì)導(dǎo)致產(chǎn)量和與溫度相關(guān)的啟動(dòng)問(wèn)題.理想和穩(wěn)健的OA大于20,以解決最終解決方案的電路板偏差,以及晶體層面的器件間和批次間差異;以及SoC.

功耗因素

現(xiàn)代SOC的設(shè)計(jì)特別注重在振蕩器電路中實(shí)現(xiàn)低電流.他們使用自動(dòng)增益控制或可選增益設(shè)置來(lái)將振蕩幅度設(shè)置得盡可能低,同時(shí)保持可靠的石英晶體振蕩器(高OA).公平地說(shuō),電路效率得到了很好的優(yōu)化.然而,由于晶體本身造成的功率損耗通常被忽略,這一因素可能很重要.參考圖3,運(yùn)動(dòng)電阻Rm會(huì)因流經(jīng)電阻的電流循環(huán)而導(dǎo)致功耗.當(dāng)CL較大時(shí),電流增加.因此,當(dāng)Rm和CL同時(shí)降低時(shí),功耗最低.

TXC晶振,貼片晶振,7M晶振

TXC晶振,貼片晶振,7M晶振 TXC晶振,貼片晶振,7S晶振

TXC晶振,貼片晶振,7S晶振 TXC晶振,貼片晶振,7A晶振

TXC晶振,貼片晶振,7A晶振 微晶晶振,32.768K晶振,CM9V-T1A壓電石英晶體

微晶晶振,32.768K晶振,CM9V-T1A壓電石英晶體