Macrobizes的XM53-15P10FE20-XM53-T12.8M石英晶體單位的解釋

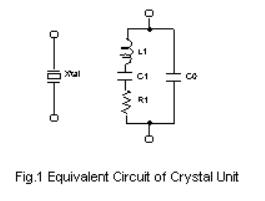

1,等效電路

晶體單元的振動實際上是機械振動。然而,如果晶體單元的行為是電轉換的,則它可以用二端網絡來表示。由L1、C1和R1組成的串聯電路與彈性振動有關,而與串聯臂并聯的C0元件則是一個電容,電容由石英晶振晶體片的電介質構成。電阻R1是晶體單元在串聯諧振頻率下的諧振電阻。(見圖1 .)

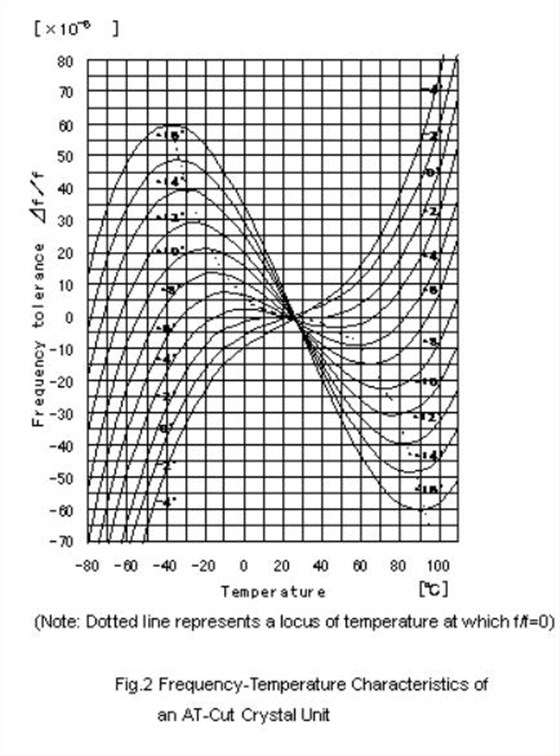

2,頻率-溫度

AT切割的特性目前最常用的AT切割晶體單元的頻率-溫度特性由三次曲線表示。(見圖2)以在給定工作溫度范圍內獲得所需頻率容差的角度切割晶片。然而,實際上,由于連續過程中切割和拋光精度的結果,表觀切割角可能存在一些差異。因此,有必要提高加工精度。

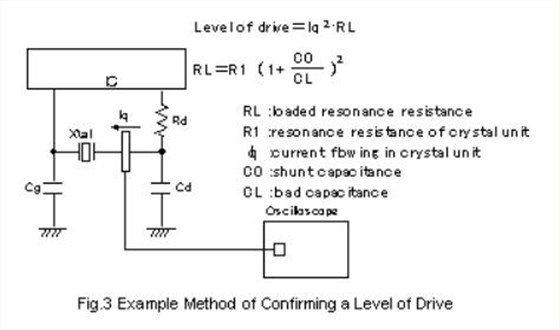

3,級驅動

由于晶體單元執行機械振動,過多的振動可能導致不穩定的振蕩頻率,并在最壞的情況下最終導致破壞。設計振蕩電路時,應檢查驅動水平,以便使用低于本公司規定水平的振蕩器。圖3示出了確認駕駛水平的示例方法。該方法采用電流探針來測量石英晶體振蕩器電流。在這種情況下,驅動級別如下:

4,負載電容

5,晶體振蕩電路的等效電路

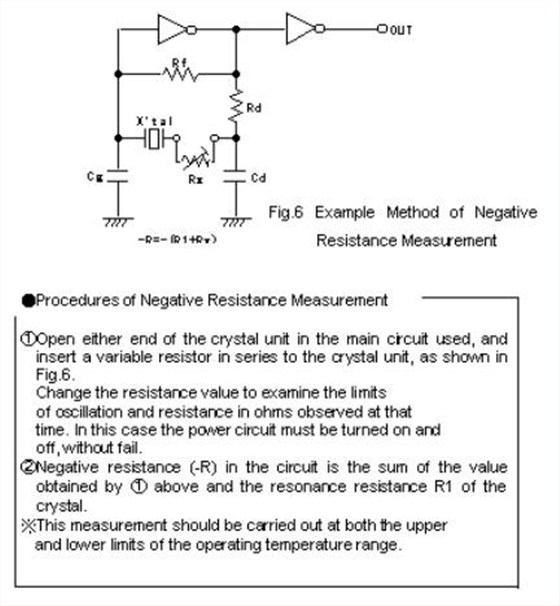

當晶體單元作為振蕩電路中的感抗被激活時,貼片晶振晶體單元和振蕩電路之間的關系如圖4所示。為了改善振蕩電路的啟動條件,最好增加振蕩電路的參數負電阻-R的值。如果負電阻容差不大(負電阻較小)的電路與具有較大諧振電阻的晶體單元組合在一起,啟動條件會變得更糟。振蕩電路應設計成負電阻值是諧振電阻的5到10倍。負載電容的中心值(用于確定振蕩頻率的絕對值)和可變范圍(振蕩頻率的微調范圍)也必須保持在振蕩電路中的最佳值。

6,振蕩電路

下面介紹由晶體單元組成的典型振蕩電路。例如,使用的元素常數。

(1)晶體單元被設計為具有100 W及以下的較低驅動限制水平。使用前,應在實際安裝電路中檢查晶體電流。(參見圖3 .)

必須檢查電路的負電阻。根據圖6可以確認負電阻。負電阻的目標是諧振電阻的5倍或更多倍。

(3)當用于C-MOS振蕩電路時,電路圖中的Rd是不可或缺的。(見圖5)。如果連接了該Rd,驅動水平將保持在規定值內,并且可以獲得穩定的振蕩頻率。

(4)Cg和Cd應在10?30pF。如果Cg和Cd在10pF以下或30pF以上使用,進口晶振,振蕩可能很容易受到電路性能的影響,驅動電平可能會增加,或者負電阻可能會降低,從而無法保持穩定的振蕩。

(5)晶體振蕩電路的布局應盡可能短。應該減少電路和接地圖案之間的雜散電容。應該避免晶體振蕩電路圖案與其他電路圖案交叉。

(6)如果使用的電路、IC類型和IC制造商不同,應確認頻率、驅動水平和負電阻。

*泛音振蕩電路需要額外咨詢

7,晶體單元應用的注意事項:

(1)當在運輸或電路板安裝時施加超過規定的過度沖擊和振動時,晶體元件有可能斷裂。當一個沖擊超過規定時,一定要做特性確認,增加一個振動。

(2)超聲波清洗可能導致晶體單元退化。

(3)在引線類型的情況下,將其留在引線基礎上并彎曲0.5或更多。

(4)極端電路板的變形有時會導致圖案脫落、端子和電極脫落、焊料裂紋。在特殊安裝后分割電路板時,請小心將其安裝在電路板曲線明顯出現的位置。

(5)盡可能選擇震動小的型號,當您使用自動裝載機時,請提前確認后使用。

(6)與JC-49/U系列相比,小晶體單元(HC-49U/S、HC-49USM、UM-1、SMD)的驅動極限水平較低,為100 w及以下。因此,在使用之前,應該在實際安裝電路中檢查晶體電流。

必須檢查電路的負電阻。根據圖6,負電阻的確認是可能的,負電阻的目標約為諧振電阻的5倍。

(8)在C-MOS振蕩電路中使用時,石英晶體振蕩器,電路圖中的Rd不可或缺(見圖5)。如果該Rd達到要求,驅動水平將保持在規定值范圍內,并且可以獲得穩定的振蕩頻率。

(10)Cg和Cd應在10~30pF范圍內使用,如果Cg和Cd在10pF以下或20pF以上使用,振蕩很容易受到電路性能的影響,驅動水平可能會增加,或者負電阻可能會降低,從而無法保持穩定振蕩。

晶體振蕩電路的布局應盡可能短。

應該減少電路和接地圖案之間的雜散電容。

應避免晶體振蕩電路圖案與其他電路圖案交叉。

(11)如果使用的電路是IC類型,并且IC制造商不同,則應確認頻率、驅動水平和負電阻。

一個以上的振蕩電路需要額外的咨詢。

TXC晶振,貼片晶振,7M晶振

TXC晶振,貼片晶振,7M晶振 TXC晶振,貼片晶振,7S晶振

TXC晶振,貼片晶振,7S晶振 TXC晶振,貼片晶振,7A晶振

TXC晶振,貼片晶振,7A晶振 微晶晶振,32.768K晶振,CM9V-T1A壓電石英晶體

微晶晶振,32.768K晶振,CM9V-T1A壓電石英晶體