時鐘晶振抖動的對產品的性能影響很大,這是我們都知曉的問題,而且其測量時鐘抖動的大小也漸漸地成為現在高速數字電路設計的一個重要組成部分.就目前而言,已經有不少的方法可以可來測量時鐘的抖動,抖動的定義是什么,該如何減少時鐘振蕩器抖動呢,下面康比電子帶領大家一起了解.

抖動定義為:

1、數字信號從其理想位置及時的重要瞬間的短期變化.

2、偏離事件的理想時間.

因此,術語"抖動"描述了系統內的定時誤差.時鐘抖動實際上并不會改變正在傳輸的信息的物理內容,只會改變傳輸信息的時間.根據情況,這可能或不影響最終解碼輸出.

抖動與漂移

時序變化分為兩類,稱為抖動和漂移

漫步:

●時間變化緩慢發生

●它是頻率為0到10Hz的抖動-漂移通常是由溫度變化引起的.

抖動:

●時鐘抖動會對系統造成許多不良影響,例如數據損壞和AC時序違規.

●定時抖動一直在降低電氣系統的性能,但是對更高數據速率和更低邏輯擺幅的驅動使人們越來越關注其特性.

●表征對于幫助定義,識別和測量抖動非常重要.需要設置合規標準和設計規范.

所有電路都會有一些徘徊,通常不會引起太多關注.另一方面,JITTER會給許多開發人員帶來許多不眠之夜.

您可能聽說過幾種類型的抖動.

周期性,周期到周期,時間間隔,確定性,隨機,模式相關,有界,正弦和高斯,但基本上它們都屬于兩類.確定性或隨機性

確定性

●有時稱為周期性抖動.抖動以循環方式重復.它取決于模式,通常由耦合到系統中的外部確定性噪聲源引起,例如開關電源噪聲或強RF載波.它也可能由不穩定的時鐘恢復PLL(鎖相環)引起.

●周期性抖動很難被拒絕,并且在大多數情況下,必須改進時鐘源以消除由周期性抖動引起的音調.

●它總是以振幅為界,具有特定的原因.

串擾-EMI

-開關電源噪聲

-同步開關輸出(SSO)

-器件功能相關性

定期

看看上面的3個信號.

●第一種是沒有抖動的理想時鐘.

●第二個信號是正在調制的時鐘.

●第三個顯示調制功能.

當函數為高時,它會增加周期長度;當函數為低時,它從時鐘32.768K的周期長度中減去.您可以看到,如果要在11個周期內進行測量,您將獲得理想時鐘和抖動時鐘的相同測量值.這就是為什么測量抖動是如此困難,并采用特殊的測試設備來完成它.

隨機抖動

隨機抖動是無法預測的定時噪聲.它沒有可辨別的模式.它會隨著時間的推移而增加,并被稱為無界限,并將影響長期可靠性.

●原因包括:

△半導體晶體結構的熱振動(噪聲).

△白噪聲(由于半規則摻雜濃度而不是完美的價電子映射)

△處理異常

△閃爍噪聲(低頻應用,通常在電阻器,二極管,晶體管和開關中找到).

測量時鐘抖動

時鐘抖動的真正衡量標準是時鐘晶振邊沿隨時間的精確位置.檢查邊緣位置的最直接方法是使用示波器.不幸的是,使用標準示波器測量的任何抖動都是由于觸發不穩定造成的.因此,即使使用非常好的示波器進行直接波形測量也不是有效的抖動測量.

使用高性能,寬帶寬示波器和高速時鐘抖動分析軟件,對于獲得良好的時鐘抖動測量至關重要.

這并不是說示波器不能用于觀察抖動.

在波形中,可以通過調整示波器以顯示一個完整的時鐘周期來估計其峰峰值.當示波器在第一個邊沿觸發時,可以在第二個邊沿上看到周期抖動.

請記住,測量的抖動總是大于電路的真實抖動,因為測量的抖動包括石英晶體振蕩器和示波器的抖動.

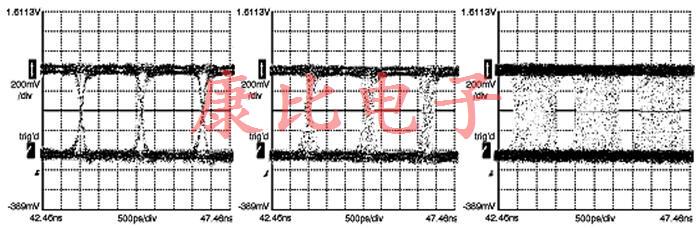

(從左到右)低抖動/高質量,中等,高抖動/低質量

通常稱為"眼圖",每個圖是由于噪聲或抖動引起的邊緣放置的累積圖形畫像.理想情況下,采樣發生在"眼睛"的中心.隨著邊緣抖動的增加,明顯的眼睛開始閉合.

數字信號傳輸質量越好,眼睛應該有更開放的白色空間.

●最終眼圖的白色空間的寬度簡單地稱為眼睛寬度.如果眼圖由足夠的樣本(數百萬和三百萬個三個時間段轉換)組成,則眼寬度是在任何給定時間段內數據線穩定的時間量的良好度量.這可以很好地了解允許的設置時間和保持時間.

●最終眼圖的白色空間的高度稱為眼高.如果眼圖由足夠的樣本組成(數百萬和數百萬個三個時間周期的過渡),則眼高可以告訴接收器的VIH和VIL需要在何處正確地采樣數據.

理想的最小抖動范圍屏幕截圖

過度的抖動屏幕截圖

減少抖動的方法

●過濾良好的電源.

△導致時鐘抖動的主要因素是設計電源中存在明顯的電壓降.器件電源和接地輸入引腳應在PCB上具有正確的布線,并始終保持穩定的石英晶振器件電壓.

●精心設計的電路板布局.

△良好的布局是關于保持噪聲電流不會交叉耦合到時鐘和信號線.需要足夠的單個地平面以防止地面反彈和虛假振蕩.

●在設計階段精心選擇時鐘

●限制設備上的I/O和CPU活動.

●為PLL電源輸入引腳提供適當的濾波

●提供清除頻率噪聲的參考時鐘.

●在時鐘抖動超出系統可接受的AC要求的系統上,將一個串聯RC OSC晶振電路(RXFC+CXFC)添加到XFC引腳以提供PLL噪聲抑制,從而可以快速恢復PLL鎖定條件以獲得更寬的頻率帶寬.

結論

總之,采用各種方法來產生時鐘振蕩器頻率.在設計階段用于確定系統需求所花費的時間將導致更少的問題,并且以后花費更少的時間來糾正它們.它還有助于確定每種應用的成本效益方法.